“.” when uploading data “ok” or “x” when using erase or single-byte write command G (Good), E (Error), also other responses ^C interrupts command processing

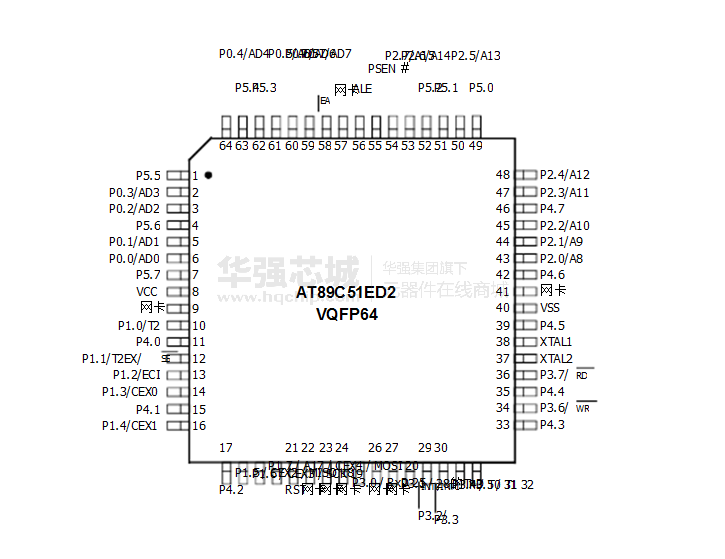

PSEN=0 & /EA=0 & RST=1 (RST must remain active)Ġ000h while in bootloader mode, F800h in normal (user) modeĬlock prescaler, reset, WDT, keyboard interface, extra 2 ports in PLCC68/VQFP64, SPIĨmux 24bit ADC, WDT, 2xUART, SPI, 16bit PWM, BOD Hw register, can be set by IAP/ISP, cleared only using parallel programmerġ28 B (transparently bytewise programmable) Sw register, independent for core and peripherals, core forced x2 mode when hw bit programmed (FX2) Sw register, independent for core and peripherals, core x2 bit loaded from hw register (HSB.X2) on reset Sw register, independent for core and peripherals EFTON - UART programmable '51 comparison chartĤ0 MHz in 12clk mode 20 MHz in 6clk (x2) modeĦ0 MHz / 40 MHz (*) in 12clk mode 30 MHz / 20 MHz(*) in 6clk (x12) mode (*) - full VDD range, incl.external code executionģ3 MHz in 12clk mode 20 MHz in 6clk (x2) mode

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed